### Tera-Pixel APS for CALICE

Progress Meeting 6<sup>th</sup> September 2006

### Main Activities

- Meeting with Foundry B

- Tender for 0.18 micron fabrication

- Phone meeting with Foundry D

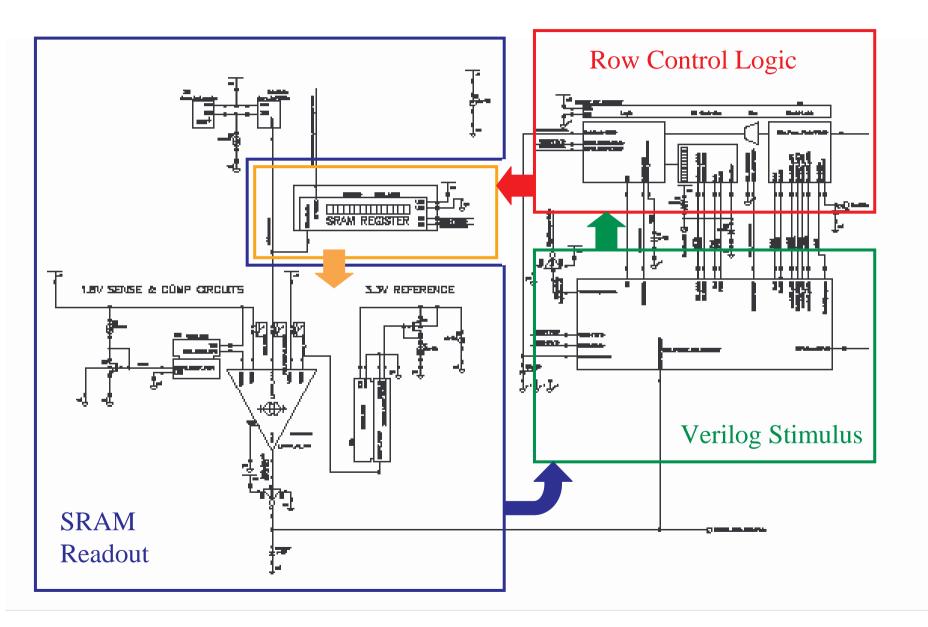

- [JC] Digital logic design & simulations

This presentation

- [RT] New analog pixel circuits

- Meeting with Guilio, Mike, Marcel & Konstantin

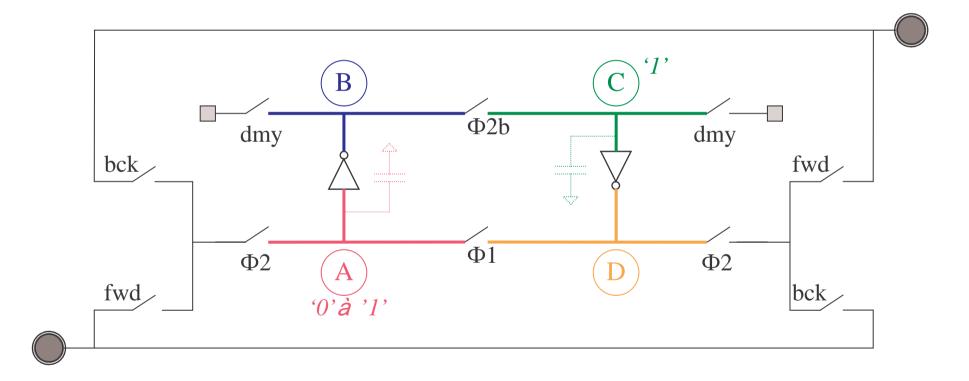

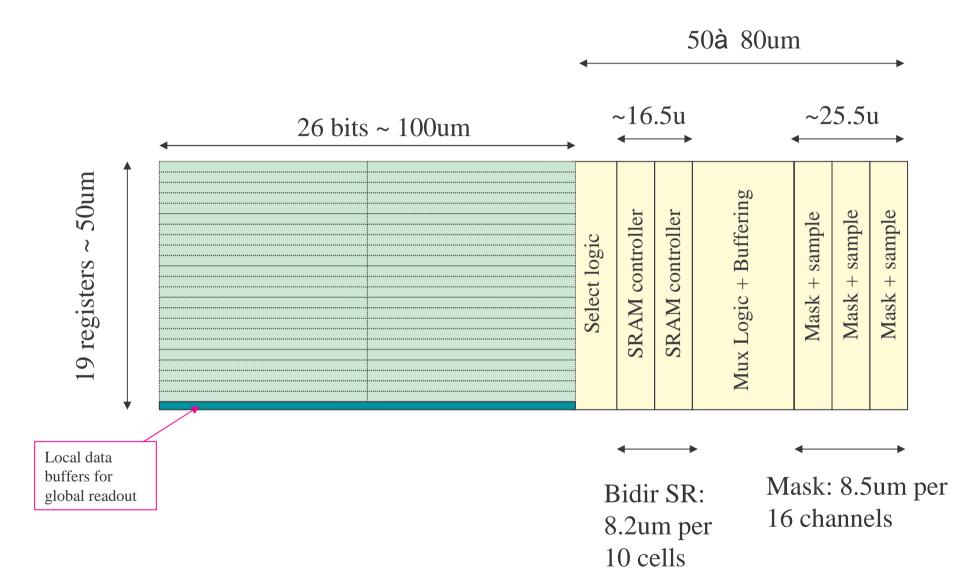

### Bidirectional SRAM Shift-Register Cell

#### Area Estimates

*Readout* + *I/O buffers*

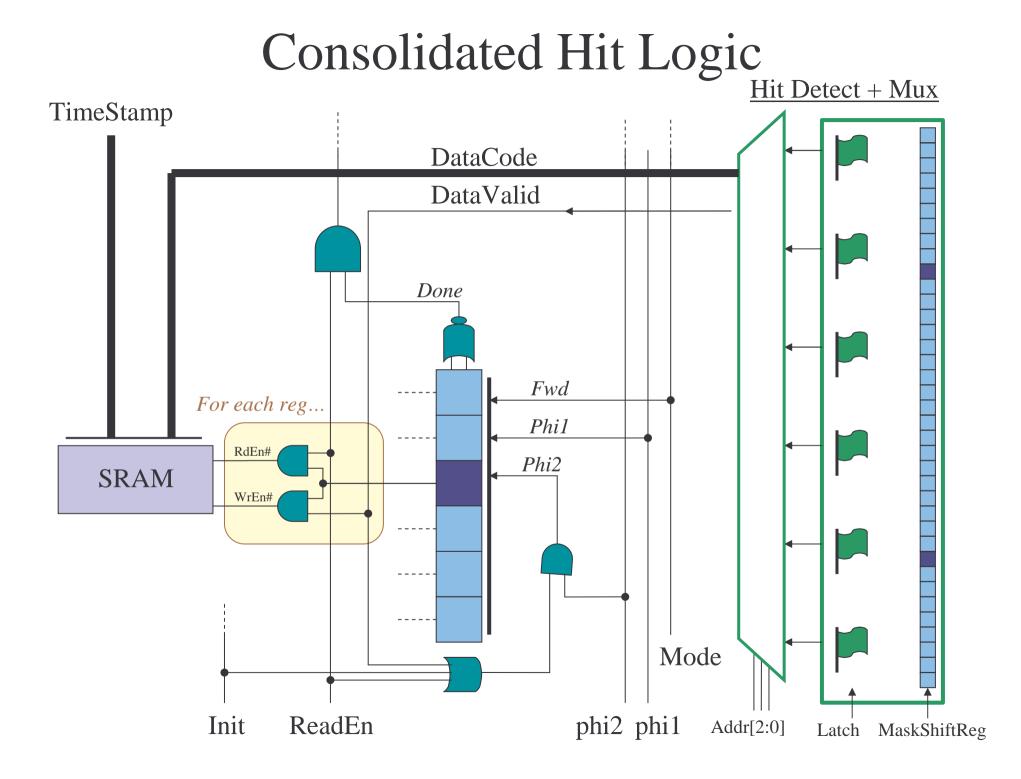

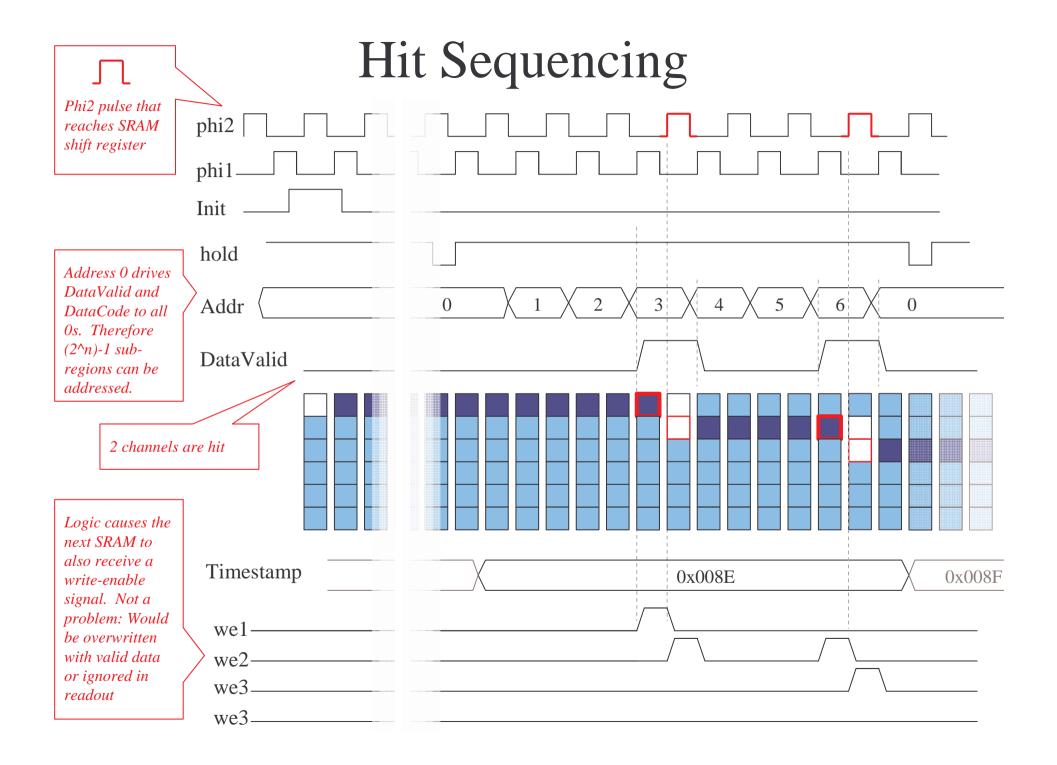

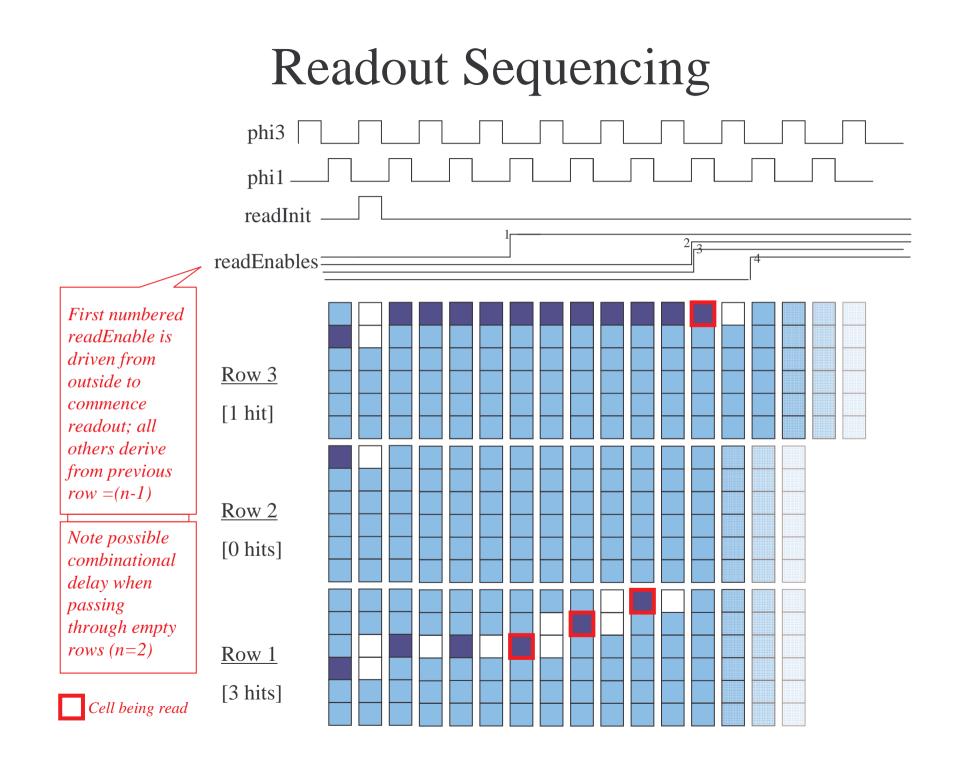

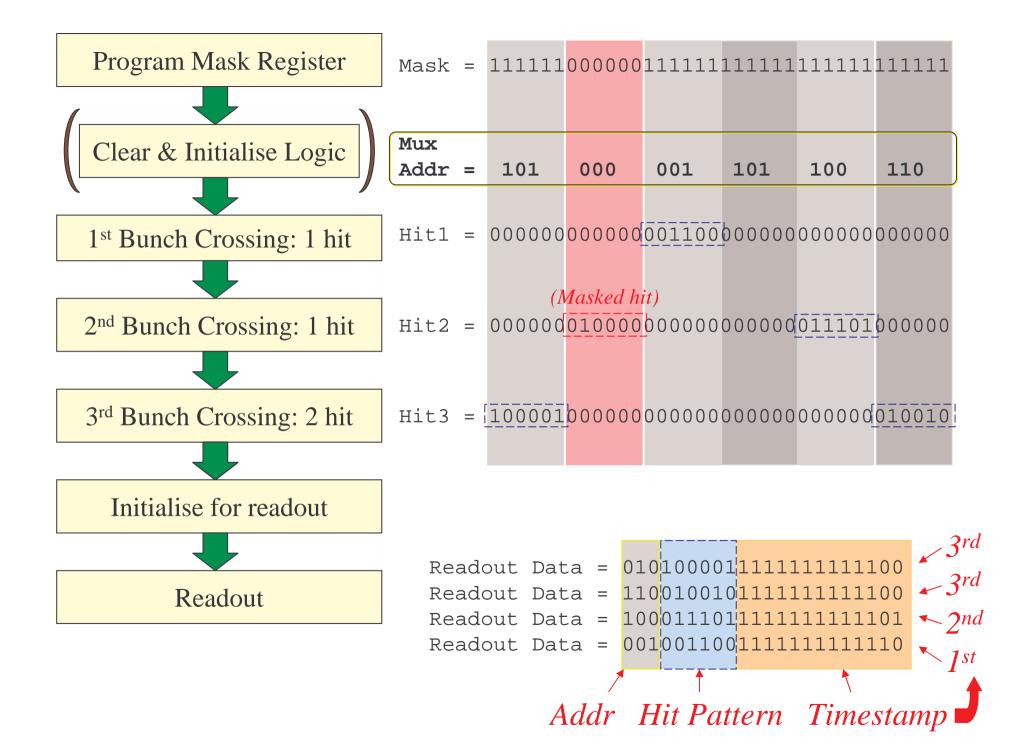

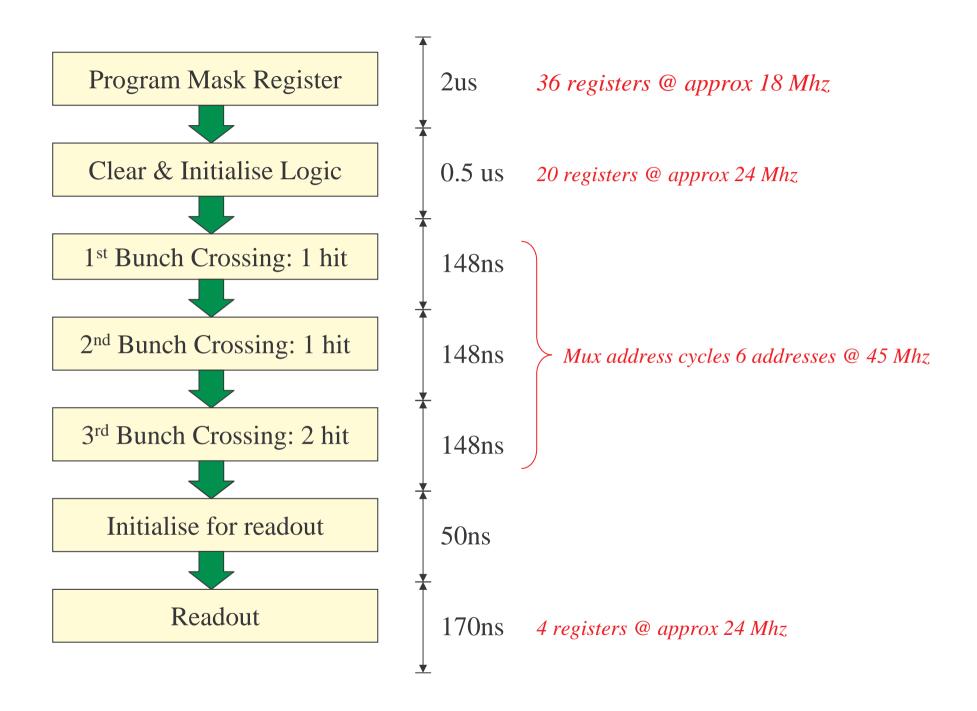

# Logic Simulation

# Questions

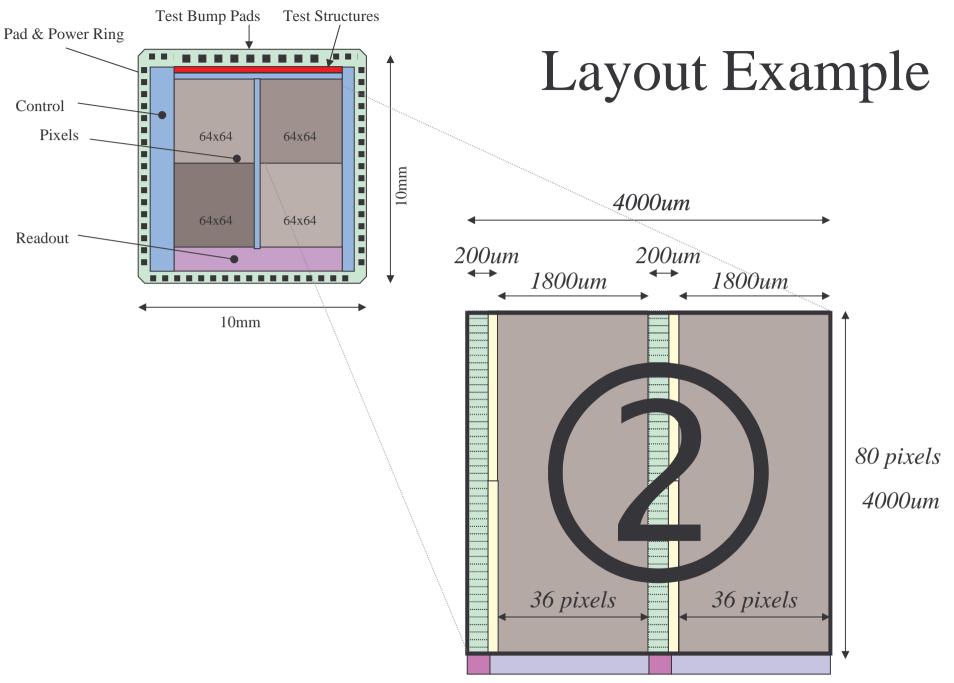

Number of sub-sets of pixels?

-6 or 7

Number of pixels in a sub-set?

-6 or 7 or 8

Currently Implemented

| $\overline{\mathbf{v}}$ | 36 pixels            | = 1800 um |

|-------------------------|----------------------|-----------|

|                         | Control logic + SRAM | = 200 um  |

|                         | (19 regs)            |           |

|                         | Dead Area            | = 10 %    |

# Question

- Assuming a row must be reset after a hit (real or noise)...

- This reset is likely to occupy the next bunch crossing, ie lasting 150ns, during which time the N pixels in this row will be 'blind' to a subsequent hit (real or noise)

- <u>Is this acceptable?</u>