#### Activities so far

Meeting at Imperial, Paul and Matt

- A part of work on preparation for testing of the ASIC1 reallocated from Matt to me:

- o Readout PCB

- o (tbc) a part of firmware for the control board

Vladimir Rajović / Birmingham

### **Readout PCB**

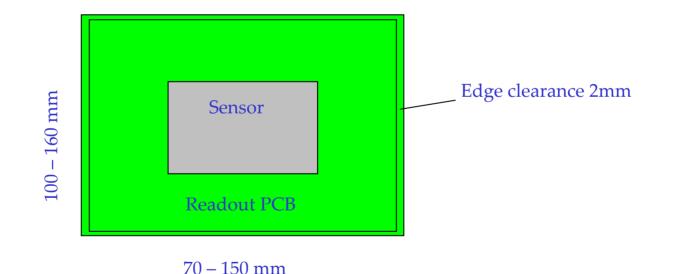

#### There are mechanical constraints, seemed not too harsh at first glance

Vladimir Rajović / Birmingham

# **Readout PCB**

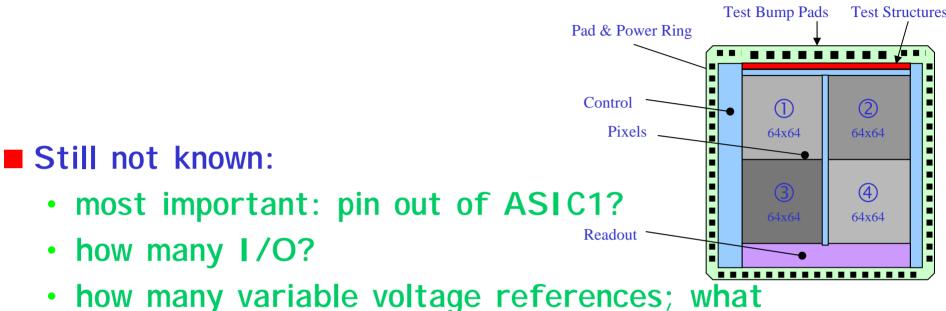

how many variable voltage references; what precision?

For the above, an input from RAL is awaited

clock, control & readout connector(s)? (to be settled down through contact with Imperial)

Vladimir Rajović / Birmingham

# **Readout PCB**

#### Preliminary working assumptions:

- 40 input + 40 output MAX

- 20 analog voltage references MAX, precision not really known, working out multiple possibilities while waiting

- linear power supplies, in order to avoid noise off switching power supplies

- Now it does not seem that relaxed regarding mechanical constraints, quite a lot of external components might be needed

- Not a problem packing them within given constraints personally would prefer more space for relaxed physical separation of LVDS, analog and digital sections of the board

Vladimir Rajović / Birmingham

# **Control Board firmware**

There is a plan that a daughter board holding 1Mx18 bit SRAM for buffering of readout data is attached to the control board

The SRAM interface firmware block is not written yet, not 100% sure whether Matt or I will write it (not really on agenda at the moment)

Vladimir Rajović / Birmingham