# Case for Support - CALICE Calorimetry for the International Linear Collider

C.G.Ainsley<sup>2</sup>, R.J.Barlow<sup>4</sup>, G.Boorman<sup>5</sup>, D.Bowerman<sup>3</sup>, J.Crooks<sup>6</sup>, P.D.Dauncey<sup>3</sup>\*, M.J.Goodrick<sup>2</sup>, B.J.Green<sup>5</sup>, M.G.Green<sup>5</sup>, C.M.Hawkes<sup>1</sup>, R.Hughes-Jones<sup>4</sup>, S.Kolya<sup>4</sup>, M.Lancaster<sup>7</sup>, G.Mavromanolakis<sup>2</sup>, N.Pezzi<sup>7</sup>, M.Postranecky<sup>7</sup>, D.R.Price<sup>3</sup>, F.Salvatore<sup>5</sup>, S.Snow<sup>4</sup>, R.J.Staley<sup>1</sup>, R.J.Thompson<sup>4</sup>, M.A.Thomson<sup>2</sup>, R.Turchetta<sup>6</sup>, M.Tyndel<sup>6</sup>, E.G.Villani<sup>6</sup>, D.R.Ward<sup>2</sup>, M.Warren<sup>7</sup>, N.K.Watson<sup>1</sup>, J.A.Wilson<sup>1</sup>, M.Wing<sup>7</sup>, O.Zorba<sup>3</sup>

<sup>1</sup>University of Birmingham, <sup>2</sup>University of Cambridge, <sup>3</sup>Imperial College London, <sup>4</sup>Manchester University, <sup>5</sup>Royal Holloway, University of London, <sup>6</sup>Rutherford Appleton Laboratory, <sup>7</sup>University College London

January 14, 2005

# **Executive Summary**

The International Linear Collider (ILC) is seen by high energy physicists in all regions of the world as the most important new project in the subject. Its physics program has been shown to complement that of the LHC; in particular the ILC will be able to perform many high precision measurements. The CALICE collaboration brings together physicists from all parts of the world who have an interest in calorimetry for an ILC detector. The immediate focus for CALICE is the construction and testing of prototypes of highly granular calorimeters, using technologies suitable for the ILC, in test beams during 2005-6. Five UK groups were approved by the PPRP at the end of 2002 to join CALICE.

The UK contribution was to provide readout electronics and DAQ software for the CALICE electromagnetic calorimeter, and also to contribute strongly to software and analysis efforts. During the past two years, the electronics has been successfully constructed and the prototype is about to move into a test beam. We have also made a leading contribution to the software work in CALICE.

The present proposal serves two main purposes. The first is to seek support for completion of the test beam campaign and analysis of the data. The second is to build on our successful contributions in CALICE and perform further generic R&D for ILC calorimetry. It is anticipated that experimental collaborations will start to form around 2008, working towards technical design reports in 2009. Our proposed R&D addresses some of the key issues which need to be attacked before that point. In this way, we intend that the UK be well placed to design and construct a substantial part of the calorimeters for an ILC detector.

The work proposed will cover the next three financial years and is divided into five (strongly interconnected) workpackages:

#### • WP1: Completion of test beam program

We request travel funds, and support for RA posts, to ensure that the UK groups participate fully in the data taking and exploitation of the data. Total cost to PPARC £0.30M.

<sup>\*</sup>Spokesperson

# • WP2: Data Acquisition

We propose several areas of generic R&D which address key issues associated with reading out a highly granular and compact detector. In particular, large data volumes must be transported reliably, in the minimum of physical space. Total cost to PPARC £0.72M.

# • WP3: Monolithic Active Pixel Sensors

We propose to investigate an attractive and novel approach for ILC electromagnetic calorimetry, namely digital readout of small pixels, building on existing UK expertise in MAPS technology. Total cost to PPARC £0.94M.

#### • WP4: Mechanical and Thermal Studies

We propose to deploy existing UK expertise to address several issues connected with heat flow and thermal modelling, and the assembly of very large silicon pad arrays. Total cost to PPARC £0.17M.

# • WP5: Simulation and Physics

We propose to build on existing leadership and expertise in these areas. We plan to continue developing tools and to perform simulation studies, especially of calorimetry, which will allow us to participate in global detector design and optimisation. Simulation expertise will also be needed by the other workpackages. Total cost to PPARC £0.35M.

As part of the support for these packages, we request five new RA posts, the continuation of the existing CALICE RA post at Cambridge, and additional effort at UCL and RAL/ID, in addition to effort already funded through rolling grants and the RAL SLA. The overall total cost to PPARC of the proposal is £2.48M, or £2.66M including the working allowance.

# Contents

| 1 | Introduction 5 |                                                                    |                 |  |

|---|----------------|--------------------------------------------------------------------|-----------------|--|

|   | 1.1            | The International Linear Collider                                  | 5               |  |

|   | 1.2            | The CALICE Collaboration                                           | 5               |  |

|   | 1.3            | General status of CALICE                                           | 6               |  |

|   | 1.4            | Background to the proposal                                         | 7               |  |

| 2 | Sta            | tus of the current UK effort                                       | 7               |  |

|   | 2.1            | Status of the UK electronics                                       | 7               |  |

|   |                | 2.1.1 Readout electronics                                          | 8               |  |

|   |                | 2.1.2 Data acquisition software                                    | 9               |  |

|   | 2.2            | Status of the UK simulation effort                                 | 10              |  |

|   |                | 2.2.1 Hadronic shower modelling                                    | 10              |  |

|   |                | 2.2.2 Pattern recognition                                          | 11              |  |

|   |                | 2.2.3 Preparation for test beam                                    | 13              |  |

|   | 2.3            | General contributions                                              | 14              |  |

|   | 2.4            | Financial status                                                   | 14              |  |

| 3 | Wo.            | rkpackage 1: Completion of CALICE test beam program                | 14              |  |

| Ĭ | 3.1            | Beam tests                                                         | 15              |  |

|   | <b>9</b>       | Task 1.1: Support for beam tests                                   | 15              |  |

|   | 3.2            | Analysis and simulation                                            | 15              |  |

|   | -              | Task 1.2: Analysis of DESY test beam data                          | 16              |  |

|   |                | Task 1.3: Analysis of FNAL test beam data                          | 17              |  |

| 4 | Wo             | rkpackage 2: Data acquisition                                      | 18              |  |

| • | 4.1            | Connection from the VFE to the FE                                  | 19              |  |

|   |                | Task 2.1: Readout of prototype VFE ASICs                           | 19              |  |

|   |                | Task 2.2: Study of data paths over 1.5 m slab                      | 19              |  |

|   | 4.2            | Connection from on- to off-detector                                | 20              |  |

|   |                | Task 2.3: Connection from on-detector to the off-detector receiver | 21              |  |

|   |                | Task 2.4: Transport of configuration, clock and control data       | $\frac{1}{21}$  |  |

|   | 4.3            | Off-detector receiver                                              | $\overline{22}$ |  |

|   | _              | Task 2.5: Prototype off-detector receiver                          | 22              |  |

| 5 | Wo             | rkpackage 3: Monolithic active pixel sensors                       | 23              |  |

| Ü | 5.1            | Introduction                                                       | 23              |  |

|   | 5.2            | MAPS concept                                                       | $\frac{23}{24}$ |  |

|   | 5.3            | MAPS concept verification                                          | 27              |  |

|   | 0.0            | Task 3.1: Sensor production and testing                            | 27              |  |

| e | <b>TX</b> 70.  | rkpackage 4: Thermal and mechanical issues                         | 28              |  |

| 6 | 6.1            | Introduction                                                       | 28              |  |

|   | 6.2            | Thermal issues                                                     | 28              |  |

|   | 0.2            | Task 4.1: Thermal studies                                          | 28              |  |

|   | 6.2            |                                                                    | $\frac{20}{29}$ |  |

|   | 6.3            | Mechanical issues                                                  | $\frac{29}{29}$ |  |

|   |                | Task 4.2: Grue studies                                             | $\frac{29}{30}$ |  |

|   |                |                                                                    |                 |  |

| 7  | Workpackage 5: Simulation and physics   | 30        |

|----|-----------------------------------------|-----------|

|    | 7.1 Introduction                        | 30        |

|    | Task 5.1: Energy Flow algorithms        | 31        |

|    | Task 5.2: Global detector design        | 32        |

|    | Task 5.3: Support of other workpackages | 32        |

|    | Task 5.4: Physics studies               | 33        |

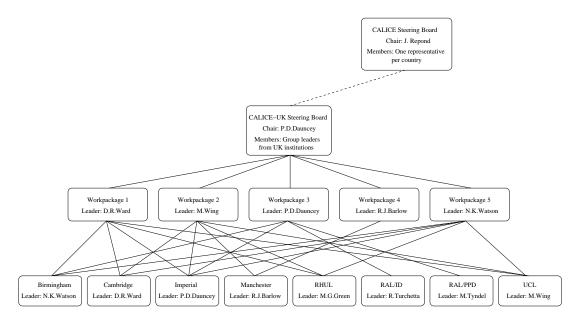

| 8  | Management plan                         | 33        |

| 9  | Benefits to the wider community         | <b>34</b> |

|    | 9.1 Relevance to PPARC science strategy | 34        |

|    | 9.2 Student benefits and training       | 35        |

|    | 9.3 Industrial benefits                 | 35        |

| 10 | ) Conclusions                           | 35        |

# 1 Introduction

# 1.1 The International Linear Collider

The International Linear Collider (ILC) [1] is a worldwide enterprise to construct an e<sup>+</sup>e<sup>-</sup> linear collider operating in the energy range 0.5 to 1 TeV. There is a widespread consensus [2] among the particle physics community that such a machine is vital for the future of the subject, and that it complements the LHC [3]. In broad-brush terms, the LHC will be a powerful discovery machine to reveal the new physics which is expected to emerge on the TeV scale in, for example, the Higgs and supersymmetry sectors, while the ILC will be better adapted to performing high precision tests.

The original accelerator R&D for the Linear Collider was centred around DESY [4], SLAC [5] and KEK [6], and viable designs were produced based both on conventional (warm) RF cavity technology and on superconducting (cold) technology. A major item of progress in the past year was the establishment of an International Technology Recommendation Panel, to advise the community on the technology to pursue. In August 2004 this panel recommended the adoption of the cold technology [7]. Efforts in all three regions are now directed towards jointly producing a fully costed accelerator technical design by 2007. For detector R&D, one important aspect of the accelerator technology choice is that it better defines the time profile of the bunch structure of the beam, with important implications for DAQ and readout.

Amongst the main physics areas to be addressed by the ILC will be precise measurements of Higgs boson properties, accurate investigation of the SUSY spectrum, probing of strong electroweak symmetry breaking, and precision top quark physics. A common requirement for most of these physics studies is good measurement of hadronic jet energies, and this places stringent requirements on the calorimetry. There is general agreement that the way to achieve the required jet energy precision is via the "Particle Flow" (aka "Energy Flow") paradigm. This requires the energy deposits of different particles in the calorimeters to be separated, which in turn leads to an emphasis on granularity and spatial resolution rather than single-particle energy resolution. These granular detectors are often referred to as "tracking calorimeters". It also demands a holistic approach to the detector design, where the interrelationship between different components of the detector is taken into account from the beginning. This is the approach taken by the CALICE collaboration.

It is expected that there will be a call for ILC detector Technical Design Reports (TDR) to be submitted in 2009. The programme proposed here should allow the UK to define its contribution to the TDR by that time. It is intended that the UK should have a clear lead in the areas where it is contributing, so as to give us influence over the future ILC detector programme.

# 1.2 The CALICE Collaboration

The CALICE collaboration [8] is undertaking a major programme of R&D into calorimetry for the ILC. It now has 167 members from 26 institutes worldwide and is by far the largest group studying calorimetry for the ILC. It is also the only collaboration within the ILC community studying both electromagnetic (ECAL) and hadronic (HCAL) calorimeters in an integrated way. We believe this overall calorimetry approach is the only way to obtain a calorimeter system which will be capable of meeting the demanding physics requirements of a high energy ILC detector. The breadth of the project and the size of the collaboration ensure that CALICE will be strongly involved in a future ILC detector.

The collaboration intends to test pre-prototypes of an electromagnetic calorimeter (ECAL) along with at least two types of hadronic calorimeter (HCAL) in electron and hadron beams over the next two years. The CALICE programme also covers simulation studies incorporating

the results of these tests, all directed towards the design of an ILC calorimeter optimised for both performance and cost. In addition, the collaboration serves as an umbrella organisation for longer-term ILC calorimeter projects where developments can be tested together.

One of the main motivations for CALICE is to verify the simulation programs, particularly for hadronic showers, such that the design and optimisation of the final ILC detector calorimeters can be done using these simulation programs with confidence. The optimisation is not purely for physics performance; for example, cost is one of the main constraints for the favoured ECAL design, which is a silicon-tungsten (Si-W) sampling calorimeter. The cost of the large area of silicon wafers required is high and so studies to reduce this cost, in terms of less area or cheaper alternatives, are a major part of this programme.

# 1.3 General status of CALICE

The CALICE ECAL prototype is a silicon-tungsten sampling calorimeter and consists of 30 layers of silicon wafers interspersed between tungsten sheets. Each wafer layer contains a  $3 \times 3$  array of silicon wafers, each containing  $36.1 \times 1$  cm<sup>2</sup> diode pads. There are around 10,000 channels in total occupying a volume of approximately  $(18 \text{ cm})^3$ . The ECAL assembly is currently paced by the silicon wafer production; more than half of the silicon wafers are now manufactured and the rest are expected over the next three months. Around one third of the layers were ready by the end of 2004 and the rest are expected to be complete by April 2005.

The analogue HCAL (AHCAL) is a sampling calorimeter with 40 layers of steel absorber sheets instrumented with scintillator tiles. The total volume is approximately  $(1 \text{ m})^3$ . The tiles are of varying sizes, with the highest granularity central region using  $3 \times 3 \text{ cm}^2$  tiles, increasing to  $12 \times 12 \text{ cm}^2$  for the outermost tiles. As the name implies, the readout will be analogue, with the off-detector electronics being common to the ECAL. The AHCAL has around 8,000 channels and is scheduled to be completed by September 2005. It is complemented by a "tail-catcher", consisting of 96 cm of iron instrumented with 16 layers of 5 mm  $\times$  5 cm scintillator strips, which will tag leakage and detect muons.

The digital HCAL (DHCAL) is a binary readout sampling calorimeter. The sensitive layers will be mainly resistive plate chambers (RPC) although for some of the tests, one or more layers may be replaced with gas electron multiplier (GEM) detectors. The RPC (or GEM) pads will be  $1 \times 1 \text{ cm}^2$ , giving 400,000 channels, each reading one bit. As one of the main aims of the beam tests is to compare the performance of these HCAL options, the same absorber structure and tail catcher as for the AHCAL will be used, so as to eliminate any spurious differences which might otherwise arise. Hence, the DHCAL is also around 1 m<sup>3</sup> in volume. The DHCAL is being developed by US groups, who are applying for funds for the readout electronics (common to RPC and GEM) early in 2005. Assuming funding is secured, the DHCAL should then be completed by summer 2006.

The first ten layers of the ECAL will be exposed to a low energy electron test beam at DESY in January 2005. This will be a technical commissioning run to debug the system and provide a first look at the ECAL performance. This test is expected to continue intermittently over the following six months as the rest of the ECAL is assembled and installed. The completed ECAL will then be run until July.

In September 2005, the ECAL will move to FNAL to take hadron beam data. Even without any HCAL behind it, it has been shown [9] that significant differences between hadronic shower models can be seen in the ECAL alone. These tests will continue until around November, when the AHCAL will be ready. The two detectors are then expected to take data for six months. Around summer 2006, the DHCAL should then arrive at FNAL and again, around six months is expected for data taking with the ECAL and DHCAL together.

# 1.4 Background to the proposal

The CALICE UK groups were approved by the PPRP in December 2002 for an initial programme with the CALICE collaboration. This was to provide the readout electronics for the ECAL and perform simulation studies. The approval covered the first two years of the CALICE programme.

The PPRP stated at the time of approval that the groups should return towards the end of the two year period to bid for continuation of the funding. The committee expected this bid to include funds both to complete the current CALICE programme as well as to define a longer-term major project which would lead more directly to the ILC detector TDRs. This is the purpose of the current proposal.

The work proposed is being done within the context of the global organisation building towards an ILC on the timescale of first collisions in 2015. In terms of calorimeters, construction is likely to take around three to four years and so would need to start early in 2012. Prototyping will require around two years prior to this, specifically 2010 and 2011. Hence, the two detector TDRs expected in 2009 will represent a major milestone in narrowing down the choices for the ILC detectors and will determine which technologies should proceed to the prototyping stage. This is why we view it as critical that the UK builds a programme over the next three years which will allow us to contribute very strongly to the TDRs.

For future planning purposes, we also wish to make the PPRP aware that there is interest in joining CALICE within the Edinburgh HEP group. They have recently had a new academic post approved specifically aimed at ILC studies and so will advertise for candidates very soon. Until this post is filled, they feel unable to commit to joining the collaboration. However, when the new lecturer is in post, then they may bid to join the UK groups with an additional proposal which would bring added value to the UK CALICE contribution. A letter from the senior members of the Edinburgh group explaining their position is attached. Note, however, that the current proposal does not assume this extra effort is available and should be evaluated on its own merits.

This proposal is organised as follows: Section 2 describes the status of the work funded in the original proposal; Sections 3 to 7 outline the five proposed workpackages for the current bid; Section 8 describes the management of the UK groups; Section 9 gives further information on benefits to the wider community. Details of the proposed workpackages and financial details are given in the annexes, together with a public outreach statement and a list of talks and proceedings.

# 2 Status of the current UK effort

We report here on the work done by the UK groups in CALICE in the last two years. The talks given and proceedings produced as a result of this work by the members of these groups over the period of the previous grant are listed in Annex E.

# 2.1 Status of the UK electronics

The UK commitment was to design, build and commission the VME readout system for the ECAL. This work was done by Imperial, RAL/ID and UCL and is essentially complete.

Upstream of the UK electronics, the signals from the silicon wafer pads are amplified and read out with the very front end (VFE) ASIC chip [10] designed by the LAL-Orsay group. The wafers and VFE chips are mounted on the VFE PCB, designed by the same group. The 60 VFE PCBs required for the full ECAL are connected to the UK electronics via mini-SCSI cables. The UK is responsible for all the readout electronics and online software downstream of the VFE PCBs.

#### 2.1.1 Readout electronics

The readout system consists of six 9U VME boards which provide the control and the digitisation of the analogue signals from the VFE PCB. They also provide local buffering of data for up to 2000 events, which should be more than sufficient for each spill. One of the boards also provides trigger logic and control, with the trigger being fanned out from this central board to the other boards in the system (including itself) using point-to-point connections on a custom-built PCB which attaches to the VME J0 connectors across the crate backplane. The maximum allowable trigger latency is set by the peaking time of the shaped VFE preamplifer signal and is around 180 ns.

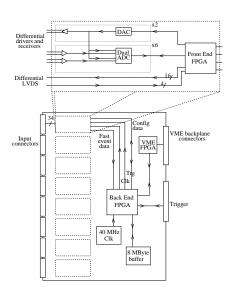

The boards were designed as a modification of the CMS silicon tracker Front End Driver (FED) design [11]. The CALICE design required a complete replacement of the FED front end (FE), which receives the input data, with a new design. The back end (BE) and VME interface were less substantially modified. Because of this commonality, there has also been some firmware shared between the two boards, reducing the engineering effort required. An overview of the structure of the CALICE boards is shown in figure 1 together with a photograph of one of the actual boards.

Figure 1: Overview of the structure (left) and photograph (right) of the VME ECAL readout boards.

Two prototype boards were fabricated by November 2003 and were thoroughly tested over the following year. These tests included a suite of stand-alone tests and calibrations using the on-board DAC. In addition, tests with the VFE PCB preproduction boards were done during early summer 2004. These involved using the DAC to calibrate the VFE PCBs, as well as using radioactive sources and cosmic rays. These tests showed that the boards were working very well [12] and only minor improvements were implemented in the design for the production versions.

Nine boards were fabricated for the production run in October 2004, of which only two were populated immediately. These two were again extensively tested before the remaining seven were released for assembly in December 2004. The seven are expected to be completed in February 2005.

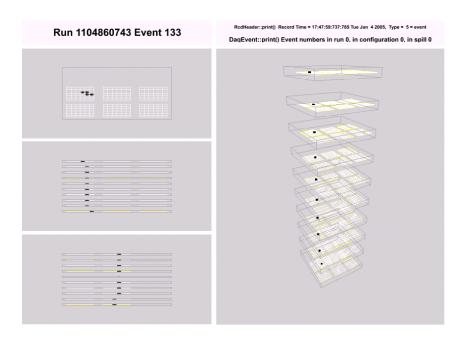

The first two production boards were taken to Paris for cosmic ray tests in December 2004. A system with ten layers of the ECAL, totalling over 2000 channels, was assembled in a cosmic teststand at Ecole Polytechnique. Data were taken using the UK boards over the Christmas

period and a total of over 1 million events were recorded. Figure 2 shows an example of an event where a clear track is seen through all ten layers of the ECAL; this indicates clearly why the phrase "tracking calorimeter" is used.

Figure 2: Example of one event of the ECAL cosmic data taken over the last month in Paris.

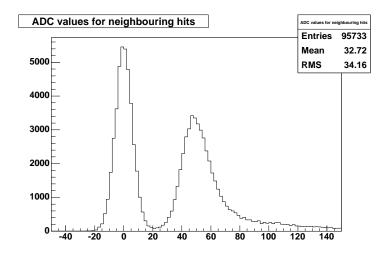

A signal/noise of around 9 for minimum ionising particles (MIP) was seen, well above the minimum requirement of 5. Figure 3 shows an example of the very clean separation of pedestal and MIP signals, where the Landau shape is visible in the latter. These data will allow the calibration for these channels to be determined to 1%, which is sufficient for the first round of ECAL studies.

The whole ECAL system has been transferred to DESY for the initial beam test which will start in January 2005 and will continue for several months.

The development of the UK boards has been seen as a major success within the collaboration. The AHCAL and tailcatcher have decided to use the same boards for their readout and are currently placing an order with RAL to produce another seven of them. This will also make the DAQ software integration easier.

#### 2.1.2 Data acquisition software

The UK groups also provided the software data acquisition (DAQ) system for the whole of the CALICE readout.

The aim of the CALICE beam tests is to collect around 10<sup>6</sup> events for each configuration of beam energy, particle, type, angle of incidence, etc. This implies a complete sample of order 10<sup>8</sup> events. To acquire this in a reasonable time, the DAQ system should achieve an average of 100 Hz readout rate. Given the spill structure at FNAL, this means an instantaneous rate during a spill of at least 1 kHz. There will be no threshold suppression applied online as studies of pedestal stability and noise are fundamental to this work. Each event is therefore expected to be around 50 kBytes in size, giving a total raw data volume of around 5 TBytes.

The DAQ software was designed from scratch to allow a very lightweight, fast system to be

Figure 3: Pedestal and minimum ionising signal peaks from the ECAL cosmic data taken over the last month in Paris.

developed which was tailored to the needs of CALICE and so capable of achieving the high rates needed. It was implemented in C++ on Linux and only uses ROOT [13] and the Hardware Access Library software from CERN [14].

The DAQ system has been used for all the UK board tests so far and has been running in the cosmics tests in Paris. The trigger rate there was limited by the physical rate of cosmics to around 1 Hz. However, in calibration runs, readout of the two production boards at rates of 150 Hz has been achieved. This implies a sustained rate with six boards of around 50 Hz would be possible now. With further firmware and software developments this is expected to be improved. The biggest limiting factor currently, however, is the CPU power of the PC being used; it is an old 400 MHz machine which has been borrowed from the Imperial group. The purchase of a faster, high-performance, multi-processor DAQ PC was included in the original bid but has been postponed until now in order to get realistic experience of the bottlenecks and requirements, as well as the best possible system for the available money. This new PC will be bought before the end of the current FY and will give large increase, of at least a factor of four, in CPU speed. Extrapolating from the rates observed now, the 100 Hz requirement should be straightforward to achieve.

# 2.2 Status of the UK simulation effort

The PPRP, when they first considered the UK groups' application to join CALICE in 2002, strongly encouraged a vigorous participation in various areas of simulation and other software, to complement our electronics contribution to the prototypes. We report here on some of the activities in this area, which were mainly produced by Birmingham and Cambridge. The PPRP recognised the importance of this field by awarding an RA post to Cambridge (filled in August 2003 by G. Mavromanolakis, who has contributed strongly to the simulation work and preparations for the test beam).

#### 2.2.1 Hadronic shower modelling

Apart from testing the hardware concepts, one of the most important goals of the CALICE test beam campaign is to gather data on the properties of showers, especially hadronic showers, in highly granular calorimeters. We therefore embarked on a program of systematic comparison between different shower packages.

The standard Monte Carlo program for simulation of the CALICE calorimeters (both for the test beam, and for the full ILC detector) is Mokka [15], which is based on Geant4 [16]. Geant4 provides a toolkit approach, whereby a variety of different interaction models can be combined in different energy ranges. The Geant4 authors provide a number of standard packages combining these models which are tailored to suit different "use cases". We have examined all those which are considered appropriate for high energy calorimetry. In addition, Mokka provides a facility for writing out a FORTRAN description of the detector geometry suitable for inclusion in a Geant3 program. In this way we gain access to the physics models available in Geant3 [17], namely Gheisha, Fluka, Gcalor and Micap. However, the old version of Fluka interfaced to Geant4 is now deprecated by the authors, and the current version is not yet interfaced to Geant4. In order to gain access to this interesting model, we have employed a package called Flugg [18], which provides an interface between the Geant4 geometry and materials, and the physics and transportation code of Fluka [19].

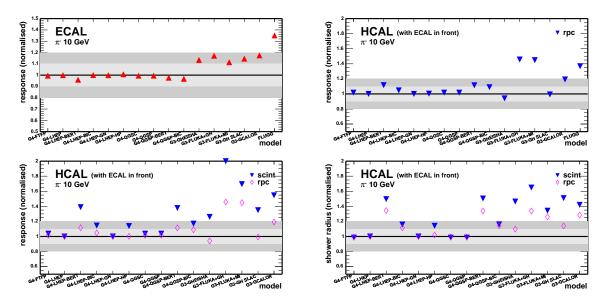

In total, seventeen different models or combinations of models have been studied [20], at different energies, for different particle species, and for two different HCAL detector technologies: scintillating tiles operated in analogue mode and RPCs operating in digital mode. Figure 4 shows some typical comparisons between these models for the case of 10 GeV  $\pi^-$  at normal incidence to the prototype calorimeter. In all cases the results have been normalised to the "LHEP" model which is the default in Mokka. A few of the significant findings are these:

- The response of the ECAL varies by up to ~ 5% between different hadronic models in Geant4. The response in Geant3 is systematically higher, but this is likely to be correlated with similar differences in the electromagnetic response seen for electron showers in the ECAL (but not for the HCAL). This is under study, but is thought largely to arise from the different algorithms used to treat multiple Coulomb scattering in each model.

- The response of the HCAL varies considerably more from model to model.

- The scintillator and RPC HCAL technologies show different levels of sensitivity to the hadronic model, with the scintillator being more sensitive. This seems largely to result from the interaction of low energy neutrons in the hydrogen-rich scintillator.

- The Flugg model shows a significantly greater ECAL response compared to the Geant models, both for hadrons and electrons; this is still under investigation, but is suspected to be associated with issues such as tracking cutoffs and precision.

- The shower width is an important determinant of the spatial resolution between showers, and we see sizeable differences between models of up to 50%. The models which use the Bertini cascade model (which is favoured by many experts) predict particularly broad showers. The scintillator HCAL is particularly sensitive to the modelling of low energy neutron transport.

All in all, these studies reinforce the need for appropriate data against which to validate these models. It may well turn out that none of the models accords with data, but this will either allow us to tune models, or to assign realistic systematic uncertainties to their predictions when optimising the final detector design.

# 2.2.2 Pattern recognition

The primary motivation for a highly granular tracking calorimeter design for an ILC detector is to separate the energy depositions of different particles within hadronic jets. This permits the use of a "Particle Flow" algorithm, in which the charged particles will be measured using the tracking chambers, and the neutrals by appropriate combinations of ECAL and HCAL

Figure 4: Comparisons between different hadronic models for 10 GeV  $\pi^-$ . In each case, the results are normalised to the predictions of the LHEP model in Geant4. The upper left figure shows the response (i.e. mean energy deposited) in the ECAL; upper right the response (number of cells hit) in the RPC DHCAL; lower left compares the tile AHCAL response with the DHCAL; lower right compares the shower radius in the two HCALs. The shaded bands denote 10% and 20% differences.

information. Experience from LEP, and early studies for the Tesla TDR, showed that this was the most promising way to achieve the  $\sim 30\%/\sqrt{E}$  jet energy resolution demanded by linear collider physics. This resolution is not driven by the intrinsic energy resolution of either calorimeter, but by the extent to which confusion between different showers can be avoided.

Such energy flow algorithms have already been written for early ILC studies. However, these codes tend to be tied to specific simulation packages and detector geometries. In view of the need to optimise global detector designs for cost and performance, it is clearly desirable to have a flexible algorithm which can readily be adapted to new setups.

A necessary first stage is to develop a versatile and robust calorimeter reconstruction algorithm. Inspection of simple event displays in the CALICE calorimeters shows that, with the 1 cm<sup>2</sup> cells and fine longitudinal sampling envisaged, substructures like tracks or small clusters are commonly observed within showers. This suggests that the optimal clustering algorithm for such a calorimeter may not be a conventional "merge contiguous hits" algorithm. Within the UK we have pursued two complementary approaches to these problems. These have been presented at several CALICE meetings and Linear Collider workshops, and been well received. Both algorithms are interfaced to the LCIO data format [21], which is becoming the agreed standard for ILC studies. In this way, it should be straightforward for others to use our code, and to integrate it with tools (such as tracking) developed elsewhere.

The first algorithm [22] takes a tracking approach. The calorimeter is treated in coaxial layered shells, automatically calculated for each geometry. Seed clusters are formed in the first layer of the calorimeter, and then hits in each layer travelling outwards are considered in turn. Each hit is compared with extrapolations of hits in previous layers, taking account of knowledge of the direction of the cluster from previous layers, and the best match found. If no acceptable match exists, a new cluster is seeded. In coding the algorithm, care is taken to encapsulate geometrical information and cuts in a single place. The algorithm was developed and tested on a variety of different samples – single particles, pairs of particles, and physics events

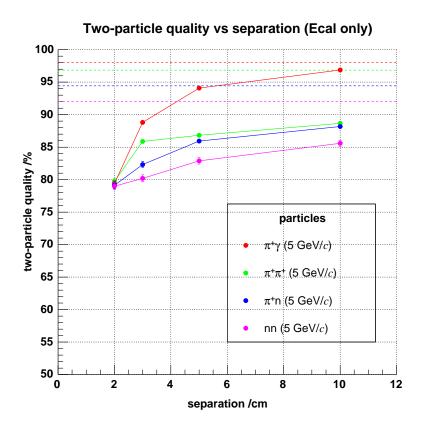

such as hadronic  $Z^0$  and  $W^+W^-$  events – simulation models and geometries. The performance seems to be quite robust. An example of the performance is given in Fig. 5. We see that photons can already be well separated from hadrons for separations above  $\sim 3-5$  cm, while the separation power is a little worse for neutral hadrons. The separation power has been found to be significantly degraded if, for example, the Bertini hadronic model, which yields wider showers (seen in Fig. 4), is used.

Figure 5: Reconstruction quality (defined as the fraction of energy which has a one-to-one relation between truth and reconstruction) for various pairs of 5 GeV particles, as a function of separation at the front of the calorimeter. The dashed lines indicate the quality for single particles, i.e. the asymptotic values at infinite separation.

The second approach to clustering [23], based on Minimal Spanning Trees (MST), is quite different. Each calorimeter hit is regarded as a node in a tree, and the MST represents the way of connecting all the nodes, with no loops, which minimises the sum of the "lengths" between nodes. Geometrical information only occurs in the metric which defines the "length", which does not have to be the geometrical distance. There are standard algorithms which efficiently compute the MST. This effectively forms the whole event into one cluster; an algorithm is then applied to form smaller clusters by cutting the tree.

# 2.2.3 Preparation for test beam

The simulation studies, comparing different models, have had a direct bearing on the test beam proposal for CALICE [24]. For example, we have examined the statistical precision required to distinguish between models, the particle species and energy regimes required. We have also performed studies of the possible usefulness of exposing the ECAL alone to a hadron beam [9]. In addition we are contributing strongly to the software infrastructure for analysis of the test

beam data. Obviously, because of our responsibilities for the DAQ, we are in a prime position to understand the data. We are also preparing the code for converting the raw data from the DAQ into LCIO format for subsequent analysis and comparison with simulation.

# 2.3 General contributions

In addition to their work directed towards the CALICE test beam, some UK members of CALICE are contributing to generic international software activities for the ILC. D.R. Ward is a convener for the Simulation group (covering simulation and reconstruction tools) for the ECFA study, and also for the worldwide LCWS workshops in Paris (April 2004) and Stanford (March 2005), while M.A. Thomson is a convener of the Global Detector Performance group for the ECFA study.

# 2.4 Financial status

The previous award was £110k for equipment, £111k of travel, 20 staff months (SM) of RAL/ID effort and two years of funding for an RA at Cambridge (the post filled by G. Mavromanolakis). There was no working allowance or contingency included in the award.

The equipment cost has come in very close to the budget. The exact total will not be known until the final seven UK boards are assembled and the high performance DAQ PC purchase is complete, but the projected total is within a few £k of the award. The remaining purchases will all be completed by the end of this FY.

Travel has been significantly underspent as the original schedule had the first FNAL test beam within the two years of the previous grant and this was a major fraction of the travel budget. This beam test has been delayed until later this year, moving it into the period of the current proposal. Again, the exact total which will be spent on travel by the end of FY04/05 is not yet known, but is estimated to be £50k.

In contrast, the staff effort needed was underestimated. RAL/ID has charged us a total of 25 SM, a 25% increase on their original estimate. This extra effort, costing around £30k, has been funded from the unused travel funds, leaving a projected £30k of travel unspent.

The RA post was filled in August 2003, which means there is almost four months of funded RA effort remaining to be used in the next FY. In addition, there was some staff effort at the Universities and RAL/PPD allocated to the CALICE ringfence beyond FY04/05, i.e. after the period of the previous approval.

However, to prevent any ambiguity, for the purposes of this proposal we ignore the unspent travel and staff funds and treat all future costs beyond this FY as part of the current bid, without assuming anything will be carried over.

# 3 Workpackage 1: Completion of CALICE test beam program

In our original 2002 application to the PPRP, we requested three years of funding to support the construction of the CALICE ECAL prototype, and its exposure to test beams with a variety of HCAL prototypes behind. In this workpackage, we are seeking the remaining funding to complete this program. This essentially consists of: travel funds to participate in test beam running and related CALICE meetings; some DAQ development effort, particularly when the HCAL detectors are integrated into the system; and staff effort so that the UK simulation expertise built over the past two years can be fully exploited in the analysis of the data.

#### 3.1 Beam tests

To support the beam tests, technical work is needed to maintain and enhance the DAQ system. This is in both the firmware for the UK readout boards and also the online software. In addition, UK personnel will need to take part in the data-taking work, participating in shifts and other activities at the beam area.

#### Task 1.1: Support for beam tests

The firmware for the readout board FPGAs is still under development. In particular, some modifications for the AHCAL will be needed and further work to increase the maximum trigger rate and reliability is needed. This should be completed within the next nine months.

The software is also still under development. The ECAL tests performed so far only required a single VME crate system, which allowed synchronisation relatively simply. However, when the AHCAL tests begin later this year, a multi-crate system will be needed, which will most likely be implemented using multiple readout PCs. This additional functionality exists but has not been extensively used and so will need to be thoroughly tested over the next six months.

The work required may be summarised in the following tasks:

- Improvement of the firmware for the reliability, speed, trigger latency and functionality. There is currently a low rate of lost triggers, thought to be due to the asynchronous trigger timing in the BE firmware and this needs to be cured in order that the readout is completely reliable. Another issue is the data readout rate; firmware work is needed to optimise the data output rate from the boards so as to be sure of achieving the 100 Hz requirement with the full system. In addition, the trigger latency is constrained to be 180 ns by the shaping time of the VFE ASIC preamplifier. While this has been achieved in the cosmics tests, it is a tight constraint and so any extra overhead which can be gained for the DESY and FNAL beam tests would be useful. Work on the trigger path in the firmware could potentially gain back at least 10 ns. Finally, extra functionality in the firmware, particularly in the trigger data buffering and readout, would allow better diagnostics and pile-up rejection.

- Enhancements of the firmware for the AHCAL are needed. Although the physical readout boards will be identical to those for the ECAL, some of the I/O signals from the front panel connectors will be used for different purposes. This requires them to have different FE firmware to drive and receive the data.

- Enhancement of the software for the AHCAL and DHCAL integration are also needed. The DAQ has been written to allow a straightforward extension to multi-PC operation, where the trigger itself is used as the synchronisation marker and unsynchronised inter-PC communication and control uses socket calls. This remains to be implemented.

- Running shifts and general maintenance of the electronics during the beam tests.

# 3.2 Analysis and simulation

The simulation work already performed in the UK has contributed significantly to the planning for CALICE test beam running. Some of the key points to emerge are as follows:

• Our broad objective is to characterise the properties of hadronic showers to 1% precision, which therefore demands samples of at least 10<sup>4</sup> events. Monte Carlo studies have shown that significant differences between models are seen with such a level of statistics.

- Differences between the predictions of models have been seen over a wide energy of energies, from 1 to 50 GeV. This is therefore the range of hadron energies we would wish to study, which covers the range of typical energies of hadrons in jets at the ILC.

- The differences between models are different for baryons and mesons. It is therefore desirable to obtain data with both proton and pion beams. We have checked that the effects seen in Monte Carlo for neutral hadrons are similar to those for charged hadrons.

- We shall wish to perform position scans across the calorimeters (probably by exploiting the natural width of the beam) and to record data at several angles of incidence in the range  $0^{\circ}$  to  $45^{\circ}$ .

This work divides naturally into two phases – tests of the ECAL alone in an electron beam, and combined tests with the CALICE HCAL prototypes in hadron beams.

# Task 1.2: Analysis of DESY test beam data

The CALICE ECAL prototype is being moved to an electron test beam at DESY in January 2005. We expect the complete prototype to be fully equipped by April 2005. The data taking at DESY will continue beyond this, with the completed calorimeter taking data up to July 2005. During this period, we shall record electron data with energies in the range 1–6 GeV. This phase of operation will be of great importance in commissioning the hardware, and in starting to understand the problems associated with real data.

In addition, the data analysis will clearly continue through much of 2005. The electron beam data, together with cosmic muons, will be of great importance in understanding the detector response, and in tuning the Monte Carlo to describe it. The current Monte Carlo describes the raw dE/dx energy deposits in the silicon pads, but clearly the UK groups will have a key rôle to play in adding realistic simulation of electronics effects such as noise and crosstalk. First versions of this exist [25], but will require tuning and adjustment in the light of experience.

The electron data will also be of importance in tuning parameters of the Monte Carlo simulations. Our early studies have shown that the simulated detector response is somewhat sensitive to details of the low-energy particle transport (such as tracking cutoffs or the precision with which multiple scattering is followed); these details can easily change the response by a few percent. Before assessing the hadronic response, it will be important to tune the simulations to model the electromagnetic response in data.

The generation of preliminary Monte Carlo samples, the establishment of an analysis framework, and first comparisons between data and Monte Carlo will already have been done by the end of FY04/05. The remaining work required may be summarised in the following tasks:

- Understand the properties of the DESY beam; implement a realistic simulation of the beam and of the beam defining detectors (MWPCs).

- Understand and tune the detector response in the light of real data. In particular the UK groups will be needed to simulate the behaviour of the electronics, building on existing work [25].

- Generation of sizeable Monte Carlo samples will then be able to begin. This will use RAL CSF as well as CPU resources in the Universities. Work is also starting at Imperial to port the simulation code to the Grid.

- Continue data and Monte Carlo comparisons throughout. The aim is to ensure that both Geant3 and Geant4, and probably Fluka, are all tuned so as to be capable of describing the electromagnetic response (electrons and muons) of the CALICE ECAL.

• Publish the results of this work, along with a technical description of the detector.

#### Task 1.3: Analysis of FNAL test beam data

CALICE has applied to Fermilab [26] for time on the MTBF (Meson Test Beam Facility) test beam. This is a recently commissioned, general purpose facility which can provide a proton beam of 120 GeV and secondary hadron beams in the energy range  $\sim 5-80$  GeV, matching our needs well. The secondary beam will contain both pions and protons, and is equipped with Čerenkov counters for particle identification, and MWPCs for beam definition. Electrons should also be available.

Our present expectation is that we shall expose the ECAL prototype in the Fermilab beam in autumn 2005. For this run, it will be placed in front of the analogue HCAL prototype and a tail catcher, so as to provide complete instrumentation of hadronic showers. For this configuration, we shall wish to record samples of data, typically of order 10<sup>6</sup> events, over a wide range of energies, for example 10-15 energy points ranging from 5 to 50 GeV. In addition, data at non-normal incidence should be recorded at a few energies.

As part of the preparations for the test beam, we have also performed studies [9] which demonstrate that, in the unlikely event that there are problems or delays with the HCAL prototypes, an exposure of the ECAL prototype to a hadron beam (particularly if additional tungsten absorbers were placed in front) would yield valuable information, especially for low energy hadrons. It is also important, of course, to record data on the performance of the Si-W ECAL in higher energy electron beams than available at DESY.

A key part of the CALICE programme is to compare different detector technologies for the HCAL. Specifically, RPCs and GEMs with digital readout are being designed. The main limitation on this is funding for the RPC electronics (which would also be used for the GEMs), and for this reason we envisage that the digital HCAL tests will not occur until 2006. We shall have a clear responsibility to keep our DAQ and electronics working throughout the test beam program, and an obvious intellectual interest in contributing to the interpretation of the results, using our expertise in the simulation area. We can therefore envisage some limited activity continuing well into 2007.

The work required may be summarised in the following tasks:

- Maintainenance of our capability of using the Geant3, Geant4 and Fluka hadronic codes, and also of using relevant new models which become available in Geant4.

- Understand the properties of the hadron beam, and how to use the beam detectors for particle identification and definition of the beam position. We shall need to implement a realistic simulation of the beam, and of the beam defining detectors (MWPCs and Čerenkovs).

- Generation of sizeable Monte Carlo samples. This will use RAL CSF as well as CPU resources in the Universities and on the Grid.

- Comparison of data and Monte Carlo, for many different hadronic models. Tuning of beam simulation and detector response as required, and iteration. This process will clearly start as soon as data are recorded, with the aim of identifying those models which provide an adequate description of data.

- Repeat the above tasks for the digital HCAL.

- Publication of findings on the properties of hadronic showers, and on comparisons with models.

# 4 Workpackage 2: Data acquisition

The design [4] for an ECAL calorimeter for a future ILC detector poses challenges to the data acquisition system (DAQ) mainly due to the large number of channels to be read out. In this work package we propose to address some of the key issues envisaged.

A generic scenario for the DAQ system is as follows. Mechanically, the calorimeter will consist of around 6000 slabs, each of length  $1.5\,\mathrm{m}$ , and each containing about 4000 silicon diode pads of  $1\times1\,\mathrm{cm}^2$ , giving a total of  $\sim24\,\mathrm{million}$  pads. At the very front end (VFE), ASIC chips will be mounted close to the silicon wafers. The ASICs will perform pre-amplification and shaping and should also digitise the data and may even apply threshold suppression. The current design [27] for such chips has 16 channels, although this may be higher in the final calorimeter. The data will be digitised in the ASIC and the data transferred to the front-end (FE) electronics which are placed inside the detector at the end of the slab. It is expected that threshold suppression will be done at the FE in FPGAs to reduce the data volume significantly. The data will then be transferred, probably via a switch, to an off-detector receiver which may be PCI cards in a PC farm.

If we assume the bunch timing of the 800 GeV TESLA design, the following parameters have to be considered. There will be a bunch crossing every 176 ns, with 4886 crossings in a bunch train, giving a bunch train length of about 860  $\mu$ s. The bunch train period is 250 ms, giving a duty factor between trains of about 0.35%.

In a shower, up to 100 particles/mm<sup>2</sup> can be expected, which in a  $1\times1\,\mathrm{cm}^2$  pad equates to 10,000 minimum ionising particle deposits. The ADC therefore needs a dynamic range of 14 bits. Assuming 2 bytes per pad per sample, then the raw data per bunch train is  $24\cdot10^6\times4886\times2=250\,\mathrm{GBytes}$  which equates to 0.3–2.5 MBytes for each ASIC (assuming they each process between 32 and 256 channels, as expected for the final design). These data are generated within a bunch train length of 860  $\mu$ s giving a potential data rate out of the ASIC of 0.4–3 GBytes/s. Threshold suppression and/or buffering (to allow readout between bunch trains) within the ASIC could reduce this rate. However, suppression in the ASIC may not be flexible enough compared with doing this in the FE and buffering requires some ASIC power to remain on between bunch trains, potentially generating too much heat. Hence the rates after the VFE depend on the assumptions and system layout and will be discussed for each individual case where necessary.

In this proposal, DAQ equipment will be developed which attacks likely bottlenecks in the future system and is also sufficiently generic to provide the readout for new prototype calorimeters. Alternative designs of a DAQ system which could affect the layout of the final detector or functionality of components are also considered. For example we consider a setup where more information is processed on the ASIC or off the detector and hence there is no need for FE electronics. This could save space, and hence cost, and reduce the amount of heat dissipated inside the detector.

The proposal is split into five tasks which investigate the three principal stages of the DAQ system: the connection from the VFE to the FE; the connection from the on- to off-detector; and the off-detector receiver. A strong under-pinning thread here is to attempt to make use of commercial components and identify any problems with this approach.

The programme detailed below will allow us to continue assisting development of new technologies for the DAQ system. We would expect to write a chapter in the future technical design report on the DAQ system for the calorimeter. For the final calorimeter, the DAQ should ideally be the same for the ECAL and HCAL. Although CALICE-UK has so far concentrated on the ECAL, our proposals for R&D contained in this document are sufficiently generic that both calorimeter sections should be able to converge to use the DAQ system we design. This will place us in a leading position to build the DAQ system for future large-scale prototype calorimeters

# 4.1 Connection from the VFE to the FE

There are two tasks within this area.

# Task 2.1: Readout of prototype VFE ASICs

The current version of the VFE ASIC chip [10] is being used to read out the existing CALICE ECAL. This chip does not meet the requirements for the ILC ECAL and the development of the design is an ongoing project in LAL/Orsay. In the next 1–2 years, they expect to have a version of such a chip with low enough power and noise that would serve as a realistic prototype. This ASIC is expected to have 16 channels, an internal ADC per channel, multiple gain ranges, and optional threshold suppression and digital buffering to reduce the required output rate. They expect to submit the ASIC for a fabrication round roughly once per year in early summer. We propose to build simple readout systems to study these ASICs.

The steps in this task are as follows:

- The LAL/Orsay group produce single-ASIC PCBs to study the chip performance. They will supply us with some of these PCBs with chips from each production round. This will allow us to understand the chip clocking and control.

- We propose to design build a PCB to hold at least 32 chips, thereby reading out about 500 channels. This would need to use the threshold or buffering option to keep the rate low enough for straightforward readout.

- We will then mount and test multiple VFE ASICs on the PCB to give us practical experience in the associated issues of clock, control and configuration of these prototypes in bulk, as well as allowing studies of pedestal and noise stability. How these chips behave will significantly influence the design (and cost) of the final on-detector DAQ readout system and so early data here will be invaluable.

A similar PCB readout system as used to readout the MAPS PCBs (as detailed in Section 5) would be used, thereby consolidating firmware effort. This UK activity is obviously paced by the work of the LAL/Orsay design team so is anticipated that activity will start in the middle of the second financial year but will be mainly concentrated in the final year.

#### Task 2.2: Study of data paths over 1.5 m slab

If threshold suppression or buffering could be done in the VFE ASIC, the rate to the FE would be reduced by two orders of magnitude. Current designs cannot do this and it may not even be desirable or practical, so we have to allow for data rates of order GByte/s needing to be transferred out of each VFE ASIC during the bunch train. Whether an electrical or optical connection would be needed has to be investigated. Although chip-to-chip fibres are not yet standard technology, this is an active area of industrial research [28].

The construction of a 1.5 m long fully operational calorimeter prototype is unlikely on timescales of the next few years. However, issues of how the data would be transported from the VFE to FE have to be considered and can be done already without a real prototype. Transporting of order GByte/s of data over 1.5 m in a very limited space is a challenge. The conventional approach would be to use copper but here the effects of noise and interference will have to be considered. There is also the possibility of using optical fibres although here there are also design considerations: the size of connectors would have to be investigated as the vertical clearance at the VFE is of the order of mm and the power needed to transmit light out would also need to

be investigated. This work ties in closely with the mechanical and thermal aspects of the design as discussed in Section 6.

The steps in this task are as follows:

- In preparation for a real prototype, we propose to build a test system with a 1.5 m PCB containing FPGAs to emulate the VFE and FE, linked electrically. This would begin with two 500 mm PCBs for initial tests and investigations before moving onto three 1600 mm PCBs for final tests.

- The bandwidth and cross-talk of the data transfer will be simulated using CAD tools and compared with measurements from the PCBs.

- The clock and control distribution from the front-end to the VFE chips will be investigated to determine whether one transmission line per chip is needed or multi-drop is possible.

This task would run over the three years of the proposal.

#### 4.2 Connection from on- to off-detector

In this section, we consider two possible scenarios:

Standard Configuration. In our assumed standard detector configuration, communication from the VFE will pass via the electronics at the FE to an off-detector receiver. We assume that threshold suppression will be done at the FE, and hence the rate would be significantly reduced from that at the VFE. Assuming that the rate is reduced to 1% of the original data volume of 250 GBytes per bunch train and each sample above threshold needs channel and timing label, the total data volume to be read out from the calorimeter is about 5 GBytes or about 1 MByte per slab. These data have to be read out within a bunch train period of 250 ms, giving a rate of 5 MBytes/s.

Alternative configuration. Here we imagine that the FE is removed and the communication is directly from the VFE to the off-detector. The need for FE electronics becomes questionable if more processing is done on the ASIC chip, such as threshold suppression. In such a scenario, transporting the data directly from the ASIC off the detector could be done and so the FE would become redundant. The number of fibres required to read-out the 24 million channels would vary between 750 000 to about 90 000 depending on whether the ASIC handles 32 or 256 channels. If we assume that the diameter of a fibre is 150  $\mu$ m, or with cladding 250  $\mu$ m then if half of the circumference of 12 m had fibres running along it, the bundle would be up to 1 cm in depth, but could be as little as 1 mm, depending on the number of ASICs and hence fibres. This would leave ample room for other cables and power supplies. This concept would revolutionise the whole calorimeter design and so needs to be considered now when changes in its general structure could be considered. Our research in this area will provide important feedback to groups designing the ASIC chips.

The off-detector receiver, as described later, is assumed to consist of PCI cards housed in PCs. As PCs are not 100% reliable, a switch will be necessary to send data efficiently to working PCs. The standard scenario would require less high-speed equipment off the detector, whereas the alternative would require many optical fibres with dedicated optical switching. The alternative scenario would, however, remove material from inside the detector which would ease construction and have a potentially advantageous impact on event reconstruction and, hence, physics measurements. It would also reduce the number of processing components within the detector which could be attractive since they would be inaccessible for long periods of time.

#### Task 2.3: Connection from on-detector to the off-detector receiver

We propose to set up a test system to validate the effectiveness of high-rate switching. This will investigate the issues in directing multiple 10 Gbit data flows with the linear collider time structure to high-performance processors.

The steps in this task are as follows:

- The test system will consist of four 10 Gbit ethernet interfaces each housed in a high-performance PC. These will be connected to six 1 Gbit ethernet PCs capable of driving data through the system. The 1 Gbit network interface cards will be a mixture of different cards and characterising them will be part of the goals of the project.

- After building the system, a series of tests will be done. Firstly the network interface cards, motherboards and network switch will be characterised considering jitter, latency, throughput, etc.. Then simple data flows will be examined for different scenarios. Finally the data flow will be examined for rates expected from the accelerator timing structure.

- To investigate the alternative, we propose to set up a test system to validate the use of fibres to transport the necessary data rates from the VFE to the off-detector receiver and to ascertain whether an optical ("layer-1") switch can re-route data with high efficiency. The test setup would contain a bundle of fibres coming into a switch from an effective VFE. A bundle would then come out of the switch to the off-detector receiver. The off-detector receiver, to be produced as part of Task 2.5, would be a set of PCI cards housed in PCs. The same PCI card would be used in our test system to emulate the VFE chip.

- The optical switch efficiency would then be tested when PCs fail and the data have to be swapped to another PC. Also if a PC contains a large amount of interesting data and takes up a large amount of processing time, a busy signal would be sent to the optical switch which would again re-route new incoming data. As it is assumed that some clustering will be done on the PCI cards, overlaps in geometrical areas of the calorimeter will be necessary. Therefore, the optical switch would also have to be able to send the same data to different PCs. The test system would consist of an optical switch connected via optical fibres to the PCI cards housed in PCs. We assume scalability of the optical switch, so we would use a relatively small 16×16 lane switch.

#### Task 2.4: Transport of configuration, clock and control data

In a scenario requiring an FPGA on-detector at the front end, it is imperative that the device can be re-configured remotely. This is necessary not only because of the number of FPGAs but also because of the uncertainty in the detector performance, in terms of data suppression, pedestal drifts, bad channel identification etc., all of which have to be implemented in the FE FPGA. The optimal algorithms for these tasks will only be determined after some experience of operating the calorimeter. However, this is complicated by the relative inaccessibility of the devices so that a failsafe system is required. To facilitate this, some sort of non-volatile memory that boots the device into a communicative state, or an external control system that provides an interface between the unconfigured FPGA and the outside world is required. Using devices with non-volatile memories built-in may have advantages here, but increased cost and limited re-programming cycles make these less attractive. Questions surrounding the reliability in the detector environment of these memories over the lifetime of an experiment also need to be addressed. In contrast modern SRAM-based FPGAs boast that they can re-configured infinitely and can therefore be 'refreshed' at regular intervals to ensure their configuration is not corrupted. The option of running with different firmware for different types of run is also

attractive. Reducing the number of components on the front-end-module would be advantageous from a cost, reliability and dead material point of view. In this task we propose to research a means of connecting a commercial network receiver package to an FPGA with the absolute minimum of components, so as to reliably reset and configure the device remotely.

To ensure the on-detector electronics captures data from actual collisions all components in a detector system need to be synchronised to a bunch-crossing clock. Although a 'triggerless' system is envisaged it is still useful to consider a signal that moderates readout, such as 'bunch-train-start' signal. One of the scenarios considered in this proposal makes use of standard network protocols to tag data at the front-end such that a commercial network can deliver it to a waiting event-builder PC. To co-ordinate this requires that busy information from the event-builder system is used to derive available data destinations that needs to be sent to the front-end. This can be called a trigger ID at some level. Although the need to build a large scale system is still some way off, the means of interfacing these time-dependent signals into the more asynchronous commercial network arena needs to be understood. The aim of this task is to investigate means of distributing clock and control signals using commercial networking equipment and components, as opposed to a more traditional bespoke system. This couples well with the work of investigating the FPGA fails afe in that it attempts to minimise components and connections on the front-end-module. In many ways this will be an investigation to verify that a single clock, control and configuration system can be constructed using a commercial hardware for both receiver and transmitter hardware. Although it is envisaged that fibre optic will be the dominant communications technology in a final design, lower speed copper based systems are sufficiently similar to allow the first stage of development to use this technology.

The steps in this task are as follows:

- We will consider a literature survey of the response of various FPGAs to radiation and rates of single event upsets and how to circumvent them.

- A simple test system for the failsafe studies will be set up, requiring a PC with a network card and a development board with cables and connectors.

- The clock and control test system will build on the previous FPGA failsafe work and use much of the same equipment. Additional network cards, a fanout board and switch will be required.

# 4.3 Off-detector receiver

An ideal system would have all data from the detector for each bunch train sent directly to a single PC where full event reconstruction would be performed. However, considering that the calorimeter alone will contain more than 20 million channels, even after data suppression this seems unfeasible.

It would, however, probably be desirable to get as much of the calorimeter into one processor as possible. This would permit local clustering which could be used as an input to full event reconstruction later. The fundamental questions to be answered are how much of the calorimeter can be received into one PC and how much needs to be received to make local clustering effective. The impact this has on full event reconstruction and on simulated physics needs to be evaluated. This task therefore involves a combination of hardware and simulation work.

# Task 2.5: Prototype off-detector receiver

We propose a system comprising PCI cards mounted in PCs. These cards will be capable of performing local clustering, as well as being able to be reconfigured to act as data transitters to

excercise the receivers. Recent developments in PCI cards have led to high bandwidth which is scalable due to future increases in the number of lanes using PCI Express technology.

The steps in this task are as follows:

- We will use cards based on this technology using a PCI Express bus. We propose to design and build our own PCI card to provide maximal flexibility for the tests we wish to perform.

- We would build a test system consisting of 4 PCs each with a PCI card in them and the possibility to move PCI cards between PCs so as to maximise the data rate to a single computer. To act as the VFE or FE sending the data, 4 further PCI cards would be required, housed in two PCs. Two rounds of prototyping of two cards would be done before building the final eight. In the test system, they would also be used to emulate the VFE or FE sending data off detector.

- In conjunction with the network workpackages discussed previously, tests will be made to see how efficiently data are transferred if a PC is unreachable or busy. Although it is hard to predict what technology will be available for the final system, gaining experience of cutting-edge technologies now, such as PCI Express, will prove valuable for estimates of how much data can realistically be received by each computer. So, whilst not trying to absolutely maximise the amount of data which can be transferred into a PC in the test system, the model should be scalable.

- With sufficient data transported to one computer local clustering and removal of isolated hits can be performed before full event reconstruction is done offline. This would involved firmware programming of the FPGA on the PCI card, its simulation and subsequent effect on full reconstruction and performance in a physics analysis.

# 5 Workpackage 3: Monolithic active pixel sensors

# 5.1 Introduction

All studies for a Si-W ECAL for the ILC currently consider diode pads as the sensitive elements in the silicon wafer. However, mainly outside the ILC community, work on monolithic active pixel sensors (MAPS) has developed this technology to a level of maturity such that they can now be considered as a possible alternative. The main goal of this workpackage is to study the use of MAPS for an ILC ECAL and, over the three year period of the grant, to either validate this concept or show that it is not a feasible option. If MAPS are a viable alternative to diode pads, then working to this timescale would allow the UK to contribute to the detector TDR in this area and would place MAPS as a technology being considered in which the UK would have clear leadership.

MAPS have been developed over the last decade for imaging purposes, but their application to PPARC science really took off with the collaboration led by R.Turchetta. This group has been supported by PPRP seedcorn funding for the last two years [29] and this successful project has attracted interest for tracking applications not only from the vertex detector groups involved in the ILC, but also for SLHC applications. However, as far as we are aware, there is no other proposal to use MAPS in a calorimeter.

MAPS implement both the sensitive silicon detector and the readout electronics onto the same wafer, using standard commercial CMOS processes for fabrication. The actual charged particle detection is done using electron-hole creation in the epitaxial layer. This is of order  $10 \,\mu\mathrm{m}$  thick and is located immediately below the surface layer where standard CMOS circuitry can be implemented for readout. The charge liberated diffuses within the layer and is collected by contacts passing from the surface electronics to the epitaxial layer.

The basic concept which this workpackage will develop is to use MAPS with binary readout on the sensor pixels. The channel count is extremely high and so analogue readout would produce prohibitive amounts of data. By making the pixels small enough, the probability of more than one minimum ionising particle (MIP) passing through each pixel can be kept small. Hence, a single bit to indicate the presence of a MIP is sufficient information. The data would then be stored during the bunch train in memory implemented within the pixel and read out before the next train. This idea is described in more detail in the following subsection; a more complete description of the conceptual design of a MAPS ECAL can be found in [30].

# 5.2 MAPS concept

To be able to use binary readout for MAPS pixels, the probability of multiple charged particles per pixel must be small. Simulations show the density of charged particles in the core of a 500 GeV electromagetic shower is around  $100/\mathrm{mm^2}$ , which implies pixel sizes of at most  $100 \times 100 \,\mu\mathrm{m^2}$ , although an actual size of  $50 \times 50 \,\mu\mathrm{m^2}$  is more realistic. This results in a huge pixel count; for an ECAL the size of that in the TELSA TDR [4], this would be around  $10^{12}$  pixels. The only possible way to handle such a large number of channels is to do a huge amount of data processing directly at source and so build data suppression into the MAPS sensor itself. This can then reduce the data volume which needs to be stored and subsequently read off the sensor to a manageable level.

Since the MAPS sensors have similar mechanical and thermal properties to diode pad wafers, the structure of the ECAL is somewhat independent of which is used. However, since the MAPS actually measure different physical quantities and have no external readout electronics, there are several advantages to using them over diode pad wafers:

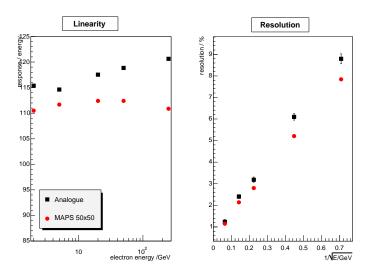

• Energy resolution. The proposed MAPS would essentially measure the number of particles passing through the silicon, rather than the energy deposition which the diode pads measure. While these two measurements would be expected to be correlated, the energy deposited is smeared out due to Landau fluctuations, non-normal incidence and the velocity dependence of the ionisation rate. Preliminary simulation studies show the higher quality MAPS information improves both the energy resolution and the linearity for electromagnetic showers from single electrons, as shown in figure 6.

Figure 6: Linearity (left) and resolution (right) of the ECAL response to electron showers as a function of the incident electron energy for an analogue (diode pad) and a MAPS calorimeter.

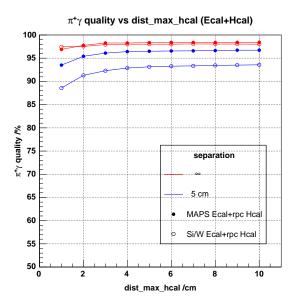

• Pattern recognition. The granularity of the MAPS ECAL is much finer than for the diode pad option, by two orders of magnitude. The natural spread of the showers prevents this from having as dramatic an impact on the cluster reconstruction, but improvements on quantities such as two cluster separation are seen in simulations, as shown in figure 7.

Figure 7: Reconstruction quality (as defined for figure 5) as a function of the main clustering cut for a diode pad and a MAPS calorimeter. The clustering algorithm was developed for the diode pad option and has not been retuned for the MAPS case.

- Size. The absence of a VFE ASIC readout chip on the detector results in a significant reduction of the VFE PCB module thickness, potentially by around a factor of two. This impacts in several areas. The gaps between the tungsten layers can be correspondingly reduced, giving a smaller shower spread between layers and hence decreasing the effective Molière radius. This contributes directly to improved pattern recognition between layers. In addition, the radial thickness of the ECAL can be reduced by around 10-20%, with a subsequent decrease in cost not only of the ECAL itself, but also of the HCAL and the solenoid magnet, both of which lie outside the ECAL. This could be a significant saving; the magnet cost alone is estimated to change by around \$2M per cm radius [31].

- Thermal issues. The main heat source in the ECAL is in the readout electronics. For the diode pad option, this is concentrated in the small, packaged VFE chip. For the MAPS option, the heat production is spread evenly over the whole surface of the bare sensor, which has an area larger by two orders of magnitude. This makes a good thermal contact much easier for the MAPS case, reducing the problem of heat removal.